ADD R1, R2, R3, i.e. Add R2 and R3, and save the result into R1so the instruction format needs to have bits set aside to identify each of the three registers.

BGT R1, R2, 100, i.e. if R1 > R2, branch the CPU to instruction at current PC + 100

LOAD R3, 4000, i.e. get the value from memory location 4000 and load it into register R3. SAVE R4, 5000, i.e. write R4's value out to memory location 5000. SET R6, 23, i.e. set R6 to the literal value 23 (not the value at location 23).

INCR R4, i.e. increment the value in R4. The Java equivalent is R4++.

| Operation | Size | Rdest | Rsrc1 | Rsrc2 |

| 6 bits | 1 bit | 3 bits | 3 bits | 3 bits |

| Inst Type | Operation | Size | Rdest | Rsrc1 | Rsrc2 |

| 0 | 5 bits | 1 bit | 3 bits | 3 bits | 3 bits |

| Inst Type | Operation | Size | Register | Literal Value |

| 10 | 2 bits | 1 bit | 3 bits | 8 bits |

| Inst Type | Operation | Size | Register | Memory Location |

| 11 | 2 bits | 1 bit | 3 bits | 24 bits |

| R3 | < | R4 | skip ahead 4 instructions |

| We Want | We Perform | The Result | Z becomes | N becomes |

| if R1 == R2 | R1 - R2 | is 0 if true | 1 if true | 0 if true |

| if R1 != R2 | R1 - R2 | is not 0 if true | 0 if true | don't care |

| if R1 < R2 | R1 - R2 | is < 0 if true | 0 if true | 1 if true |

| if R1 <= R2 | R2 - R1 | is >= 0 if true | don't care | 0 if true |

| if R1 > R2 | R1 - R2 | is > 0 if true | 0 if true | 0 if true |

| if R1 >= R2 | R1 - R2 | is >= 0 if true | don't care | 0 if true |

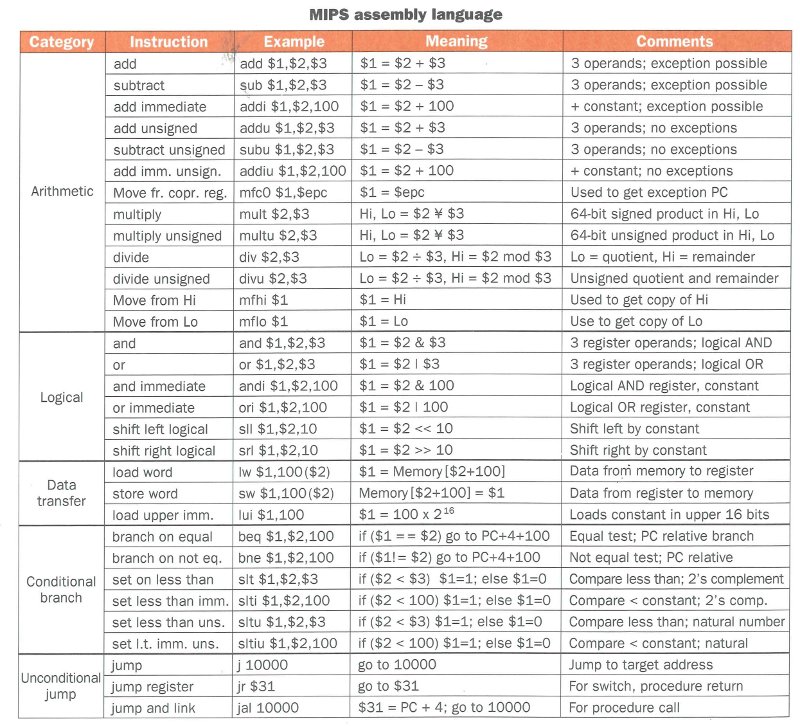

| op | rs | rt | rd | shamt | func |

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

| Instruction | op | rt | rt | rd | shamt | func |

| add $1, $2, $3 | 0 | 2 | 3 | 1 | 0 | 32 |

| addu $1, $2, $3 | 0 | 2 | 3 | 1 | 0 | 33 |

| subu $1, $2, $3 | 0 | 2 | 3 | 1 | 0 | 35 |

| mfc0 $1, $epc | 16 | 0 | 1 | 14 | 0 | 0 |

| mult $2, $3 | 0 | 2 | 3 | 0 | 0 | 24 |

| multu $2, $3 | 0 | 2 | 3 | 0 | 0 | 25 |

| div $2, $3 | 0 | 2 | 3 | 0 | 0 | 26 |

| and $1, $2, $3 | 0 | 2 | 3 | 1 | 0 | 36 |

| or $1, $2, $3 | 0 | 2 | 3 | 1 | 0 | 37 |

| op | rs | rt | address/immediate |

| 6 bits | 5 bits | 5 bits | 16 bits |

| Instruction | op | rs | rt | immed |

| addi $1, $2, 64 | 4 | 2 | 1 | 100 |

| Instruction | op | rs | rt | immed |

| lh $1, 400 | 33 | 0 | 1 | 400 |

| Instruction | op | rs | rt | immed |

| bne $19, $20, 2 | 5 | 19 | 20 | 2 |

| op | target address |

| 6 bits | 26 bits |