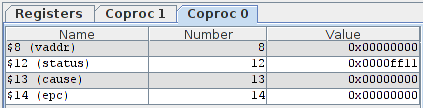

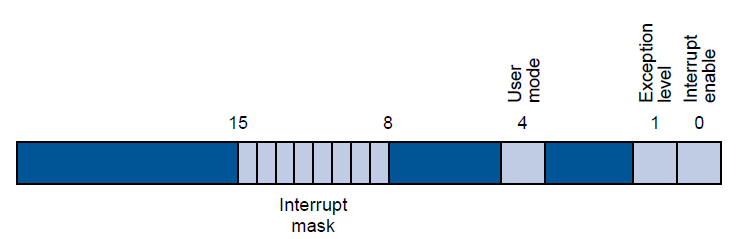

The interrupt mask field contains a bit for each of the six hardware and two software interrupt levels. A mask bit that is 1 allows interrupts at that level to interrupt the processor. A mask bit that is 0 disables interrupts at that level. When an interrupt arrives, it sets its interrupt pending bit in the Cause register, even if the mask bit is disabled. When an interrupt is pending, it will interrupt the processor when its mask bit is subsequently enabled. The user mode bit is 0 if the processor is running in kernel mode and 1 if it is running in user mode. The exception level bit is normally 0, but is set to 1 after an exception occurs. When this bit is 1, interrupts are disabled and the EPC is not updated if another exception occurs. This bit prevents an exception handler from being disturbed by an interrupt or exception, but it should be reset when the handler finishes. If the interrupt enable bit is 1, interrupts are allowed. If it is 0, they are disabled.

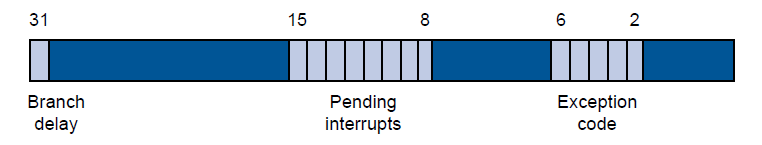

The interrupt pending bits become 1 when an interrupt is raised at a given hardware or software level. The exception code register describes the cause of an exception through the following codes:

Number Name Description 0 INT External interrupt 4 ADDRL Address error exception (load or instruction fetch) 5 ADDRS Address error exception (store) 6 IBUS Bus error (misalignment) on instruction fetch 7 DBUS Bus error on data load or store 8 SYSCALL System call 9 BKPT Breakpoint exception 10 RI Reservesd instruction exception 12 OVF Arithmetic overflow exception

NOTE: this implies that MARS does the print_int and print_string syscalls internally. Otherwise, the syscall would bring the CPU back to 0x80000180, causing an infinite recursion!